| (2)FPGA开发实战 | 您所在的位置:网站首页 › systemverilog random › (2)FPGA开发实战 |

(2)FPGA开发实战

|

文章目录

3-8译码器设计代码实现和仿真波形下节内容——半加器

3-8译码器设计

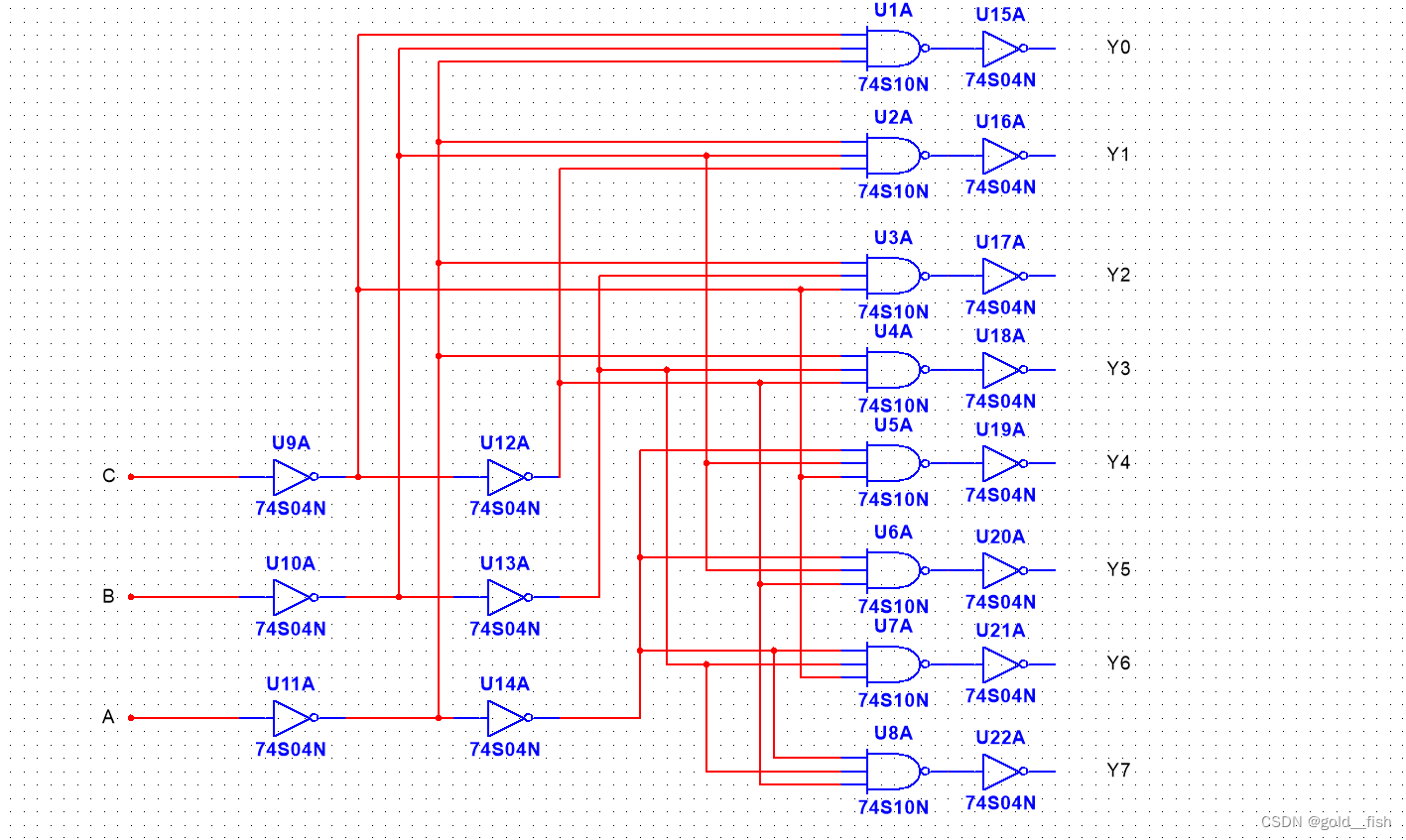

译码是编码的逆过程,在编码时,每一种二进制代码,都赋予了特定的含义,即都表示了一个确定的信号或者对象。把代码状态的特定含义翻译出来的过程叫做译码,实现译码操作的电路称为译码器。或者说,译码器是可以将输入二进制代码的状态翻译成输出信号,以表示其原来含义的电路。 译码器(decoder)是一类多输入多输出组合逻辑电路器件,其可以分为:变量译码和显示译码两类。变量译码器一般是一种较少输入变为较多输出的器件,常见的有 n 线-2^n线译码和 8421BCD 码译码两类;显示译码器用来将二进制数转换成对应的七段码,一般其可分为驱动 LED 和驱动 LCD 两类。 这里主要讲解变量译码,最常见的变量译码器为 3-8 译码器,主要用于端口的扩展。在数字电路当中常用来做地址译码。假设译码器的输入为ABC,输出则为Y0-Y7,则3-8译码器的真值表如下 ABCY0Y1Y2Y3Y4Y5Y6Y70001000000000101000000010001000000110001000010000001000101000001001100000001011100000001Y0=A’B’C’,Y1=A’B’C,Y2=A’BC’,Y3=A’BC,Y4=AB’C’,Y5=AB’C,Y6=ABC’,Y7=ABC(‘表示反变量) 用门电路设计一般为下图所示,且3-8译码器一般还会有3个附加控制端,这里没有给出。

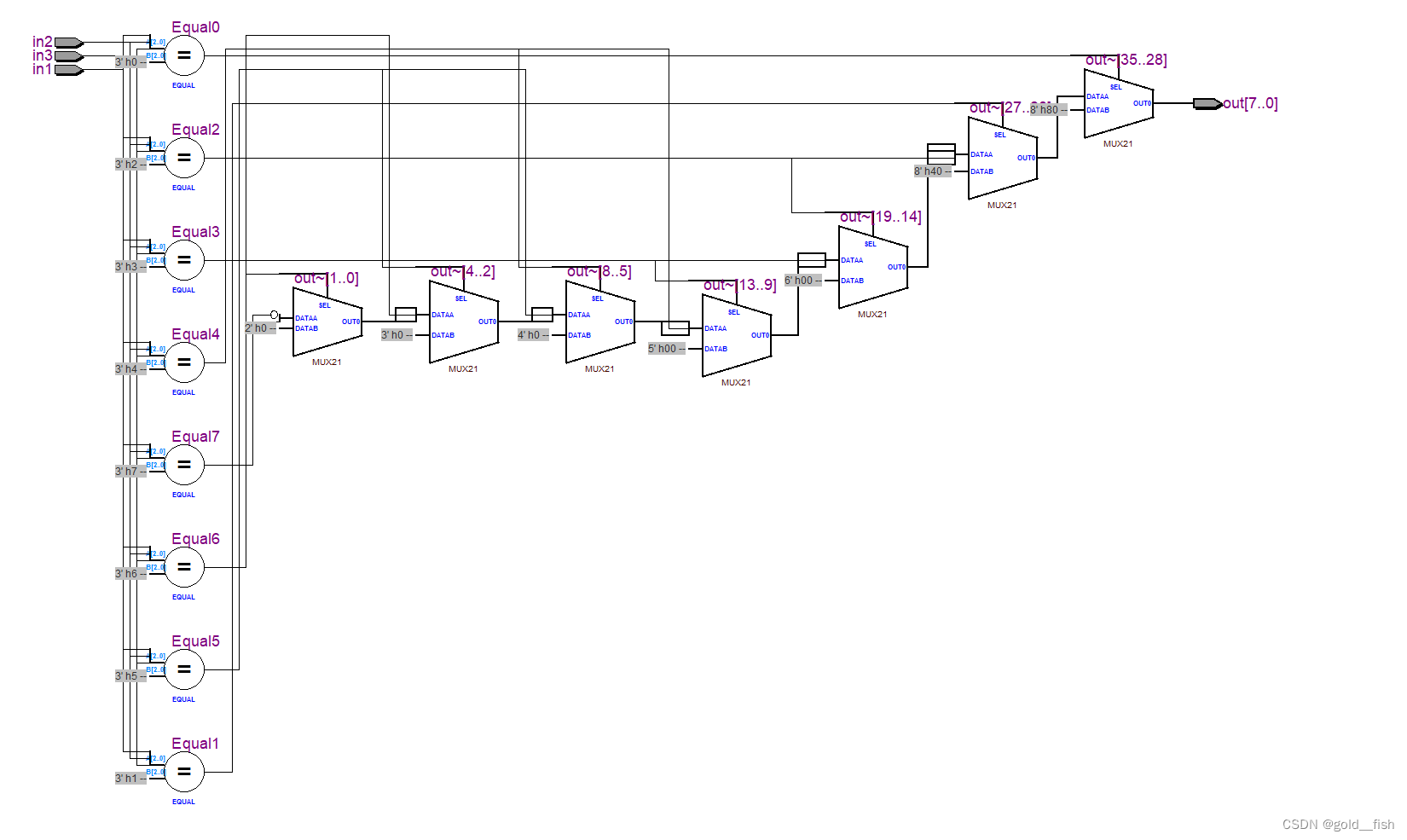

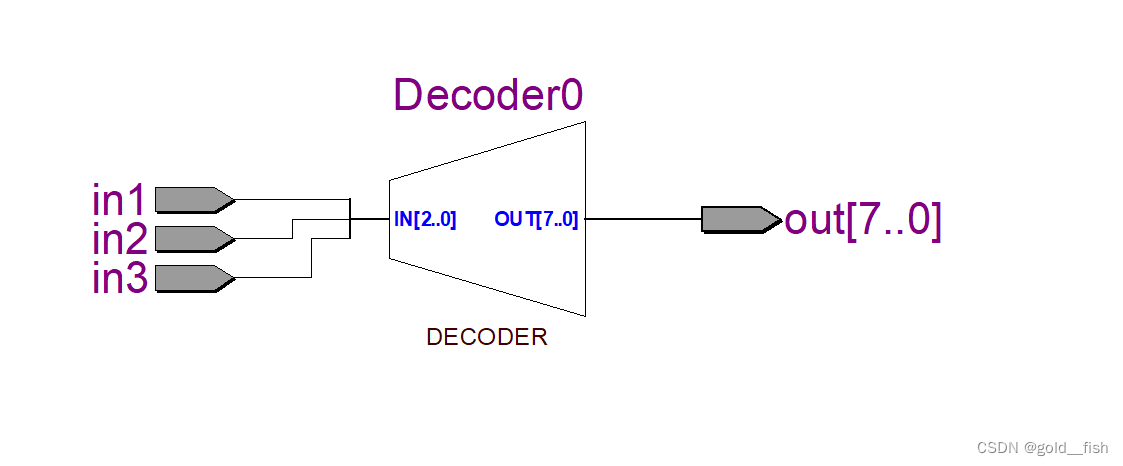

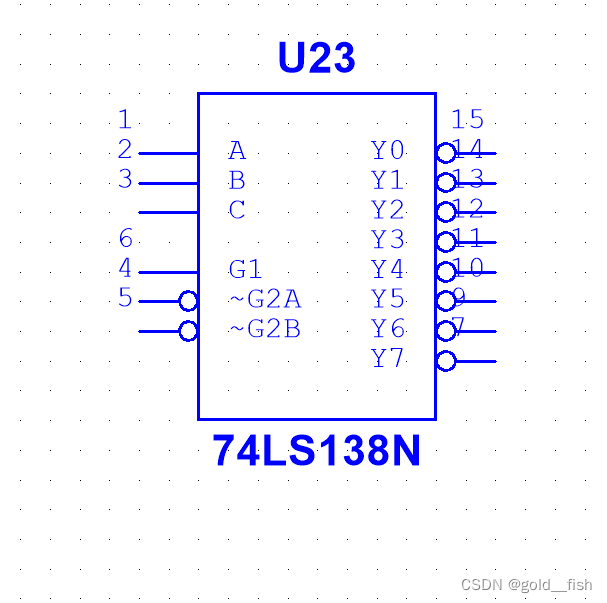

封装好的芯片如74LS138芯片管脚图如下图所示 如果不记得软件的操作和仿真设置可以点击下边链接查看。 软件的使用和仿真设置看这里 代码实现和仿真波形一、if-else语句实现 module decoder3_8( input wire in1,//输入信号in1 input wire in2,//输入信号in2 input wire in3,//输入信号in3 output reg [7:0] out//输出信号out ); out:根据 3 个输入信号选择输出对应的 8bit out 信号 always @ (*) begin//使用"{}"位拼接符将 3 个 1bit 数据按照顺序拼成一个 3bit 数据 if({in1,in2,in3}==3'b000) out=8'b0000_0001; else if({in1,in2,in3}==3'b001) out=8'b0000_0010; else if({in1,in2,in3}==3'b010) out=8'b0000_0100; else if({in1,in2,in3}==3'b011) out=8'b0000_1000; else if({in1,in2,in3}==3'b100) out=8'b0001_0000; else if({in1,in2,in3}==3'b101) out=8'b0010_0000; else if({in1,in2,in3}==3'b110) out=8'b0100_0010; else if({in1,in2,in3}==3'b111) out=8'b1000_0000; else out=8'b0000_0001; end //最后一个 else 对应的 if 中的条件只有一种情况,还可能产生以上另外的 7 种情况 //如果不加这个 else 综合器会把不符合该 if 中条件的上面另外 7 种情况都考虑进去 //会产生大量的冗余逻辑并产生 latch(锁存器),所以在组合逻辑中最后一个 if //后一定要加上 else,并任意指定一种确定的输出情况 endmoduleRTL视图

二、case语句实现(推荐) module decoder3_8 ( input wire in1 , //输入信号 in1 input wire in2 , //输入信号 in2 input wire in3 , //输入信号 in3 output reg [7:0] out //输出信号 out ); //out:根据输入的 3bit in 信号选择输出对应的 8bit out 信号 always@(*) case({in1, in2, in3}) 3'b000 : out = 8'b0000_0001; //输入与输出的 8 种译码对应关系 3'b001 : out = 8'b0000_0010; 3'b010 : out = 8'b0000_0100; 3'b011 : out = 8'b0000_1000; 3'b100 : out = 8'b0001_0000; 3'b101 : out = 8'b0010_0000; 3'b110 : out = 8'b0100_0000; 3'b111 : out = 8'b1000_0000; //因为 case 中列举了 in 所有可能输入的 8 种情况,且每种情况都有对应确定的输出 //所以此处 default 可以省略,但是为了以后因不能够完全列举而产生 latch //所以我们默认一定要加上 default,并任意指定一种确定的输出情况 default: out = 8'b0000_0001; endcase endmoduleRTL视图

三、仿真代码 `timescale 1ns/1ns module tb_decoder3_8(); wire [7:0] out; reg in1; reg in2; reg in3; //初始化输入信号 initial begin in1 |

【本文地址】

公司简介

联系我们

这里实现方式有两种:一种为if-else语句实现,判断输入ABC的情况,对应输出即可。另一种为case语句(推荐)实现。另外也会给出二者的RTL视图,读者二择一即可。

这里实现方式有两种:一种为if-else语句实现,判断输入ABC的情况,对应输出即可。另一种为case语句(推荐)实现。另外也会给出二者的RTL视图,读者二择一即可。